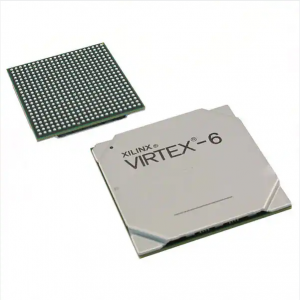

Nova kaj Originala XC6VLX240T-2FFG1759I Integra cirkvito

Produktaj Atributoj

| TIPO | PRISKRIBO |

| Kategorio | Integraj Cirkvitoj (ICoj) |

| Mfr | AMD Xilinx |

| Serio | Virtex®-6 LXT |

| Pako | Pleto |

| Produkta Statuso | Aktiva |

| Nombro de LABoj/CLBoj | 18840 |

| Nombro de Logikaj Elementoj/Ĉeloj | 241152 |

| Totalaj RAM-Bitoj | 15335424 |

| Nombro de I/O | 720 |

| Tensio - Provizo | 0.95V ~ 1.05V |

| Munta Tipo | Surfaca Monto |

| Funkcia Temperaturo | -40 °C ~ 100 °C (TJ) |

| Pako / Kazo | 1759-BBGA, FCBGA |

| Provizanta Aparato Pako | 1759-FCBGA (42.5×42.5) |

| Baza Produkta Nombro | XC6VLX240 |

Dokumentoj kaj Amaskomunikilaro

| RIMEDOTIPO | LIGO |

| Datenfolioj | Virtex-6 FPGA-Datenfolio |

| Produktaj Trejnadaj Moduloj | Virtex-6 FPGA Superrigardo |

| Media Informoj | Xiliinx RoHS Cert |

| PCN-Dezajno/Specifo | Transŝipa Senplumbo-Avizo 31/okt/2016 |

Mediaj kaj Eksportaj Klasifikoj

| ATRIBUTO | PRISKRIBO |

| RoHS-Statuso | ROHS3 Konforma |

| Humid-Senteveca Nivelo (MSL) | 4 (72 Horoj) |

| Statuso REACH | REACH Netuŝita |

| ECCN | 3A001A7A |

| HTSUS | 8542.39.0001 |

XC6VLX240T-2FFG1759I Superrigardo pri FPGA

La XC6VLX240T-2FFG1759I FPGAs estas la programebla silicia fundamento por Celitaj Dezajnaj Platformoj, kiuj liveras integrajn softvarojn kaj aparatarkomponentojn por ebligi al dizajnistoj koncentriĝi pri novigado tuj kiam ilia disvolva ciklo komenciĝas.Uzante la triageneracian ASMBL (Advanced Silicon Modular Block) kolon-bazitan arkitekturon, la Xilinx XC6VLX240T-2FFG1759I enhavas multajn enkonstruitajn sistem-nivelajn blokojn.Ĉi tiuj funkcioj permesas al logikaj dizajnistoj konstrui la plej altajn nivelojn de efikeco kaj funkcieco en siajn sistemojn bazitajn sur FPGA.Konstruita sur 40 nm pintnivela kupra proceza teknologio, XC6VLX240T-2FFG1759I FPGAs estas programebla alternativo al kutima ASIC-teknologio.ofertu la plej bonan solvon por trakti la bezonojn de alt-efikecaj logikaj dizajnistoj, alt-efikecaj DSP-dizajnistoj kaj alt-efikecaj enkonstruitaj sistemoj-dizajnistoj kun senprecedenca logiko, DSP, konektebleco kaj mildaj mikroprocesoraj kapabloj.

La serio XC6VLX240T-2FFG1759I de Xilinx FPGAs (Field Programable Gate Array) estas Virtex-6 LXT FPGA 720 I/O 1759FCBGA, Vidu Anstataŭaĵojn kaj Alternativojn kune kun datumfolioj, akcioj, prezoj de Rajtigitaj Distribuistoj ĉe FPGAkey.com, kaj vi ankaŭ povas serĉi, kaj vi povas serĉi. aliaj FPGA-produktoj.

Trajtoj

Tri subfamilioj:

Virtex-6 LXT FPGAs: Alt-efikeca logiko kun progresinta seria konektebleco

Virtex-6 SXT FPGAs: Plej alta signal-prilabora kapableco kun altnivela seria konektebleco

Virtex-6 HXT FPGAs: Plej alta bendolarĝa seria konektebleco

Kongrueco inter sub-familioj

LXT kaj SXT-aparatoj estas kongruaj piedsigno en la sama pako

Altnivela, alt-efikeca FPGA-Logiko

Reala 6-eniga serĉtabelo (LUT) teknologio

Duobla LUT5 (5-eniga LUT) opcio

LUT/duobla flip-flopparo por aplikoj postulantaj riĉan registromiksaĵon

Plibonigita envoja efikeco

64-bita (aŭ du 32-bita) distribuita LUT RAM-opcio per 6-eniga LUT

SRL32/duobla SRL16 kun registritaj eliraj opcio

Potencaj miksreĝimaj horloĝadministrantoj (MMCM)

MMCM-blokoj disponigas nul-malfruan bufradon, frekvencsintezon, horloĝ-fazan ŝanĝadon, enigjitter-filtradon, kaj faz-egalan horloĝdividadon

36-Kb bloko RAM/FIFOs

Alt-efikeca paralela SelectIO-teknologio

Altnivelaj DSP48E1 tranĉaĵoj

Flekseblaj agordaj elektoj

SPI kaj Parallel Flash-interfaco

Plurbitflua subteno kun dediĉita reagorda logiko

Aŭtomata busa larĝa detekto

Kapableco de Sistema Monitoro en ĉiuj aparatoj

Sur-blato/sen-blato termika kaj proviza tensiomonitorado

JTAG-aliro al ĉiuj monitoritaj kvantoj

Integritaj interfacblokoj por PCI Express-dezajnoj

GTX-elsendiloj: ĝis 6,6 Gb/s

Datumoj sub 480 Mb/s apogitaj per trospecimeno en FPGA-logiko.

GTH-transceptoroj: 2.488 Gb/s al pli ol 11 Gb/s

Integrita 10/100/1000 Mb/s Ethernet MAC-bloko

Subtenas 1000BASE-X PCS/PMA kaj SGMII uzante GTX-radio-ricevilojn

Elportas MII, GMII, kaj RGMII uzante SelectIO-teknologiajn rimedojn

Disponebla subteno de 2500 Mb/s

40 nm kupra CMOS-proceza teknologio

1.0V kerntensio (-1, -2, -3 rapidecgradoj nur)

Pli malalta potenco 0.9V kerna tensio-opcio (nur -1L-rapideca grado)

Alta signal-integreca flip-blata pakaĵo havebla en normaj aŭ Pb-liberaj pakaj opcioj